基本概念

各种概念的解释

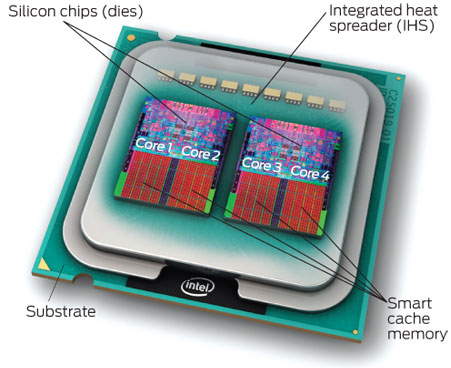

- Die 晶粒是实际的硅芯片,CPU 的所有组件(如内核、高速缓存、互连器件等)都是在晶粒上制造的。一个 CPU 封装可能包含一个或多个硅芯片。

- Core是指中央处理器内部的独立处理单元,可以读取和执行程序指令。现代 CPU 通常有多个内核,以便进行并行处理。

- Numa 非统一内存访问)--指内存访问时间取决于内核与内存位置距离的设计。在多插槽系统中,内核访问自己 CPU 插槽上的内存比访问远程插槽上的内存更快。

- Socket 插槽是主板上安装 CPU 封装的物理接口。一个插槽可安装一个多核 CPU 包。在多插槽系统中,多个 CPU 包分别插入不同的插槽

- IP Intelligent Property 将一些复杂的功能模块,如FIR滤波器、SDRAM控制器、PLL锁相环等封装好,供开发者直接调用 IP核分成三类:软核、固核与硬核。软核就是我们通常写的verilog行为描述代码,灵活性与适应性较强;固核是门级网表形式的代码,是IP的主流形式之一;硬核是GDSII版图文件,不能修改

- SOC SOC是将计算处理器和其它电子系统集成到单一芯片的集成电路。SOC 将CPU、存储器、各种接口控制模块、互联总线等集成在一起,达到减小面积、提高速度、降低功耗、节约成本等目的 SoC是在同一芯片、同一钟工艺下完成的

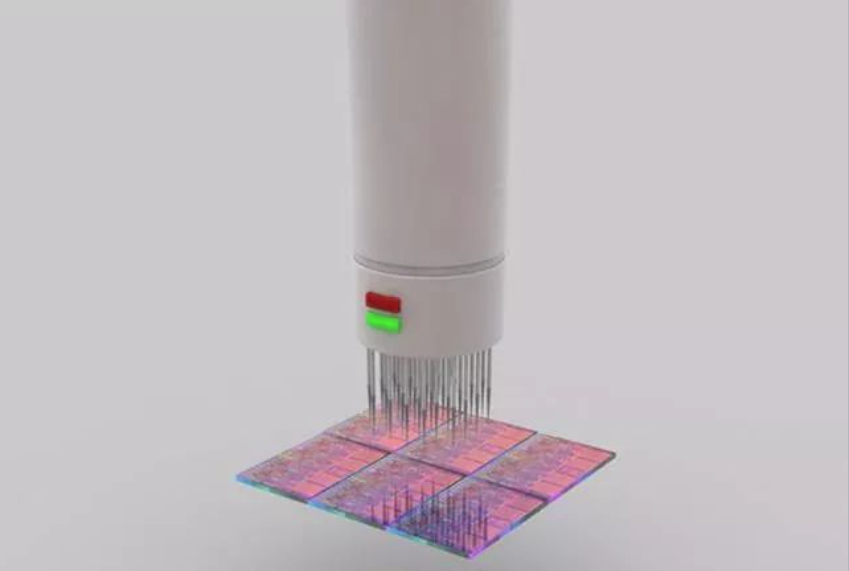

- SIP SiP是系统级封装。将处理器、存储器、FPGA等功能芯片集成在一个封装内 SiP则可以将不同工艺器件,如MEM、光学器件、射频器件等不同材质、不同工艺节点的设备垂直堆叠或水平排列,做园片级别的封装。这是超越摩尔定律的重要实现路径。

SiP的实现需要多种封装技术,如引线键合、倒装芯片、芯片堆叠、基板腔体、基板集成RF器件、埋入式电阻电容电感、硅通孔TSV等。 - Chiplet Chiplet技术就是将一个功能丰富且面积较大的芯片裸片(die)拆分成多个芯粒(chiplet),并将这些具有特定功能的芯粒通过先进封装的形式组合在一起,最终形成一个系统芯片

Die

这里是切割下来每一块就是一个die

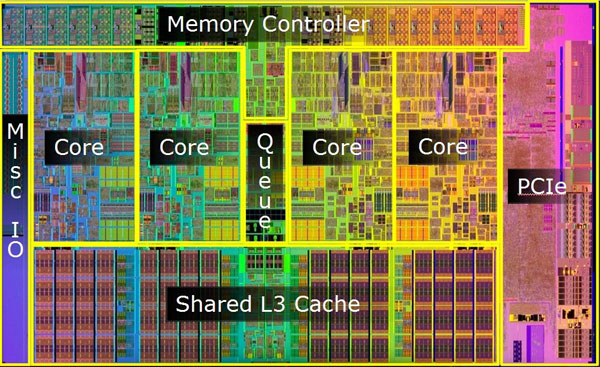

Die 和Core 之间的关系

将多个die package 封装后

CPU和Die

CPU是如何制造出来的(附高清全程图解)-腾讯云开发者社区-腾讯云 这篇文章详细讲述了如何从沙子到成品

SOC和Chiplet 技术的差异

arm N1 SOC

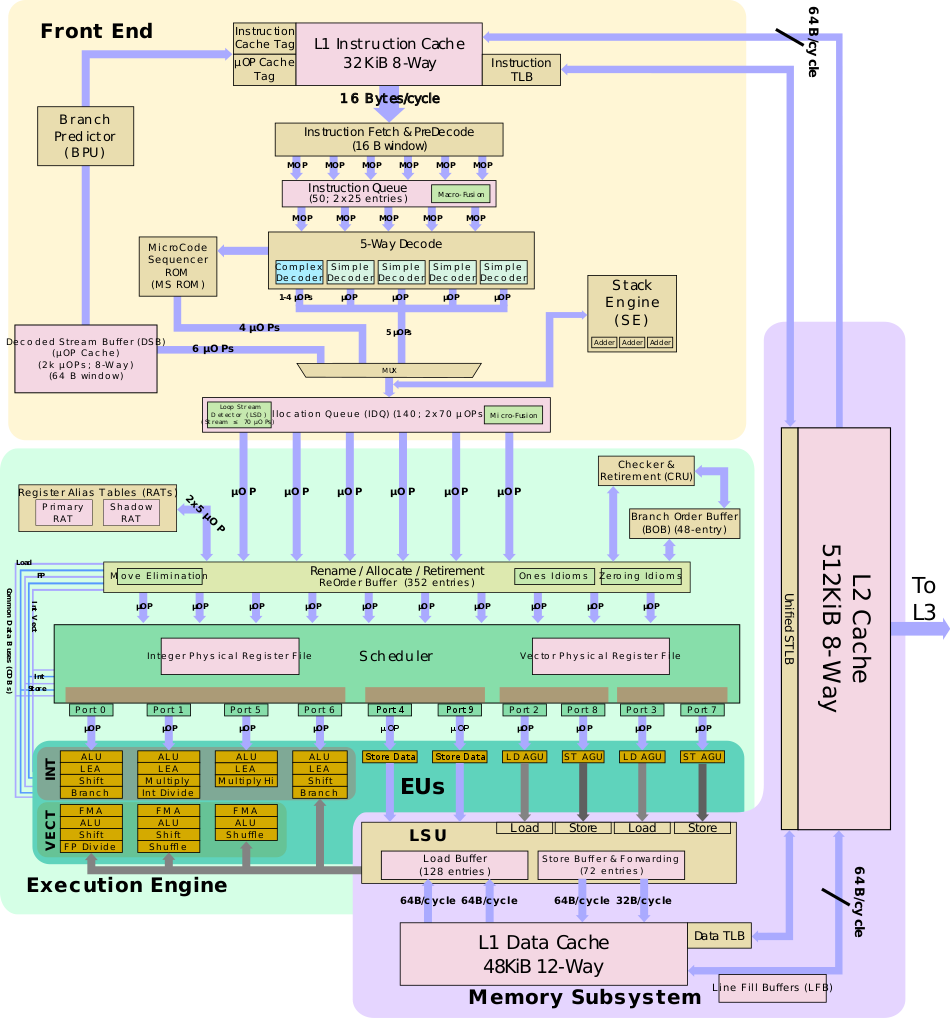

Core 内部的微架构

ARM N2

iceLake

CORE之间以及CORE和其他关系

Core 与Core 之间联系

在arm N2 SoC中所有的核、L3 缓存、内存、外设等都通过CMN700 mesh与Core互联在一起

Die和Die 之间的联系

主要通过SMP协议进行通讯 UCIE或者Partner Specific C2C PHY

Socket和Socket

CXL PHY 协议

本文由 妖言君 创作,采用 知识共享署名4.0 国际许可协议进行许可

本站文章除注明转载/出处外,均为本站原创或翻译,转载前请务必署名

最后编辑时间为: Dec 11, 2023 at 11:09 am